Dein Warenkorb ist gerade leer!

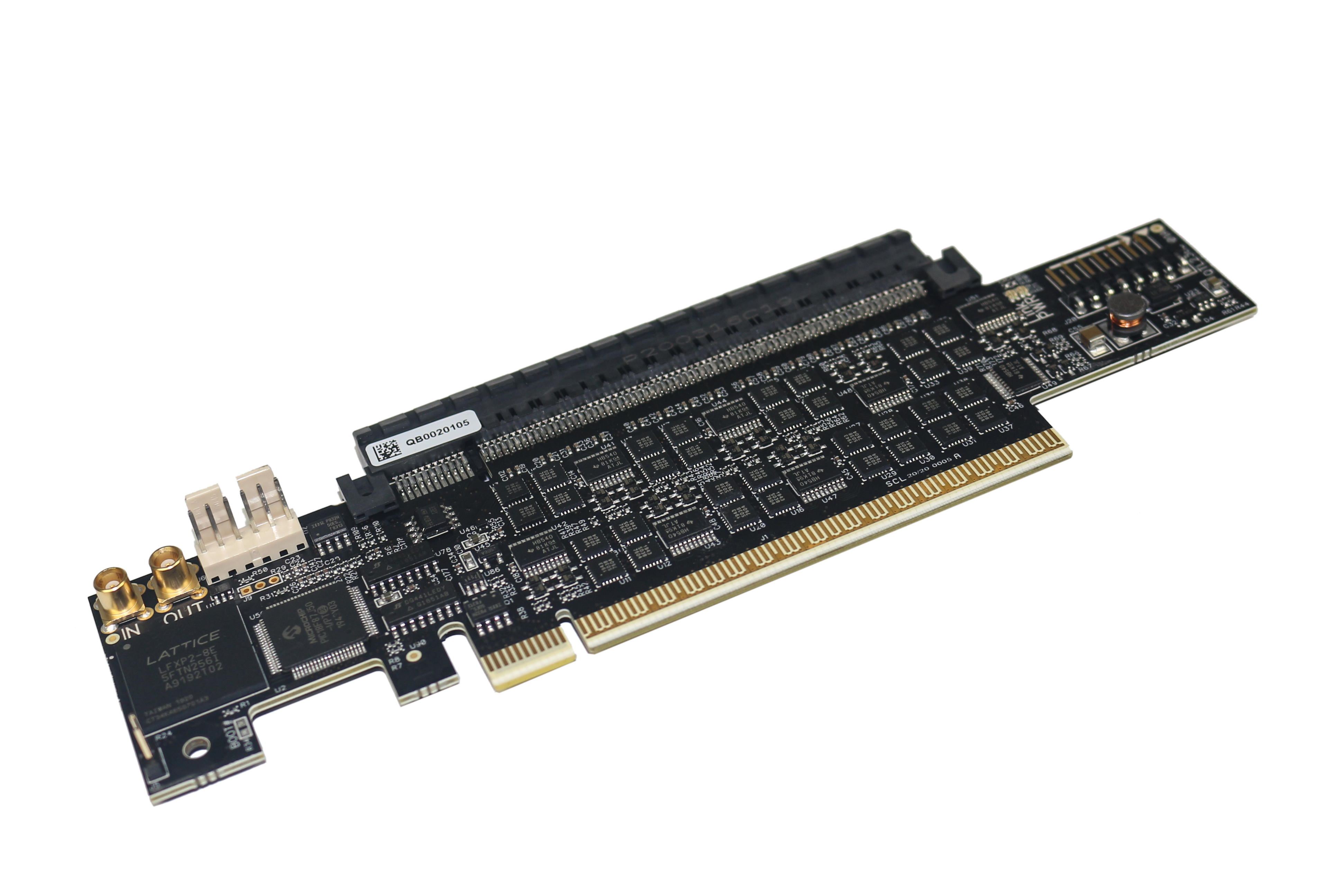

PCI Express® Gen 5: Lösung der Konformitäts- und Validierungsherausforderungen für 32 GT/s-Empfänger

Zusammenfassung Die E/A-Bandbreite von PCI Express hat sich im Durchschnitt alle drei Jahre verdoppelt, was zu einer erhöhten Nachfrage nach dieser Vollduplex-Hochgeschwindigkeitsbusarchitektur geführt hat. Mit dem Beginn der Einführung der Revision 5.0 mit einer Bitrate von 32 GT/s entstehen neue Trends und Richtlinien für die Konformität und Validierung der Empfänger. Dieses Webinar gibt einen Überblick über die Methoden zur Lösung einiger der neuen Herausforderungen bei Test- und Messempfängern für PCIE® 5.0 bei 32,0 GT/s. Die wichtigsten Themen, die in dieser Präsentation behandelt werden, sind folgende Status der 5.0-Spezifikationen, einschließlich Base, CEM und der TestspezifikationenProgramm zur Einhaltung von PCI-SIG® 5.0Herausforderungen und neueste Richtlinien für 32 GT/s-Empfängertests von BranchenexpertenFeinheiten der Kalibrierung von 32-GT/s-EmpfängernHandhabung verlustreicher Rückkanäle mit Entzerrung Überlegungen zu Rx-Tests mit und ohne Spread Spectrum Clocking (SSC)Lösung von Validierungsproblemen mit einer Empfängerlösung von Anritsu & Tektronix PCI Express, PCIE und PCI-SIG sind eingetragene Marken und/oder Dienstleistungsmarken der PCI-SIG. Redner David Bouse, Systemingenieur…

Raspberry Pi 4 Modell B 4GB

Der Raspberry Pi 4 Model B ist die vierte Generation, die von der Raspberry Foundation produziert wird. Er eignet sich nicht nur zum Erlernen von Codes, zum Anpassen und Spielen, sondern ist auch perfekt für IoT-Projekte. Raspberry Pi 4 garantiert mehr Rechenleistung, mehr Speicher und mehr Konnektivität, wobei die volle Kompatibilität mit Projekten, die mit früheren Versionen erstellt wurden, erhalten bleibt. Er ist mit einem 1,5-GHz-Quad-Core-Prozessor und einer 64-Bit-ARM-Cortex-A72-CPU ausgestattet, die eine Leistung bieten, die mit x86-PC-Systemen der Einstiegsklasse vergleichbar ist. Dual-Display-Unterstützung für Auflösungen bis zu 4K über ein Paar HDMI-Micro-Ports, 4 GB RAM, Videodekodierungs-Hardware bis zu 4Kp60, 2,4 / 5,0 GHz Dual-Band-WLAN, Bluetooth 5.0, Gigabit-Ethernet, USB 3.0, PoE (Power over Ethernet), über spezielle Add-ons für PoE-HATs. Related posts: Raspberry Pi 4 Model B 4GB SAMSUNG Galaxy Buds3 Pro (2024, ANC) wasserfest, KI-Echtzeit-Sprachdolmetscher, True Wireless Bluetooth 5.4-Ohrhörer, Hi-Fi, Geräuschunterdrückung, Touch-Steuerung, internationales Modell R630 (Silber) Portable Monitor 15.6 Inch Full…

Brauchen Sie einen Analogkomparator in Ihrer MCU?

Dieser Industriecomputer kann von einer MCU mit einem integrierten Analogkomparator profitieren. Ich weiß noch, wie ich im Elektronikunterricht an der Uni meinen ersten Analogkomparator mit einem LM358-Operationsverstärker gebaut habe. Solche einfachen Schaltungen scheinen nicht immer einen praktischen Nutzen zu haben, bis man anfängt, sie in echte Systeme für seine Kunden einzubauen. Ein analoger Komparator lässt sich leicht mit einer positiven Rückkopplung in einer Operationsverstärkerschaltung aufbauen, aber man benötigt immer etwas Platz auf der Platine mit dem Operationsverstärker-IC und zusätzlichen Komponenten in der Rückkopplungsschleife. Wie sieht es mit der Arbeit mit einem analogen Komparator und Ihrer MCU aus? Ihre MCU verfügt über zahlreiche integrierte Funktionen und E/As. Eine Möglichkeit, einen Komparatorausgang mit Ihrer MCU zu verwenden, ist einer der GPIOs. Eine bessere Möglichkeit ist die Suche nach einer MCU mit integrierter Komparatorschaltung, die eine externe Op-Amp-Schaltung oder einen Komparator-IC überflüssig macht. Im Folgenden erfahren Sie, wie diese Schaltungen in Ihrem Design…

Die besten Gaming-Motherboards im Jahr 2021

Die besten Gaming-Motherboards mit den besten Chipsätzen von Intel und AMD. Die besten Gaming-Motherboards mit den besten Chipsätzen von Intel und AMD. (Bildnachweis: Future)JUMP TO: Intel Z490Intel B460Intel Z390AMD X570AMD B550AMD A520 Das Herzstück eines jeden großartigen Gaming-PCs ist das Motherboard. Es ist das Rückgrat Ihres Systems, das alle wichtigen Komponenten enthält, die Sie benötigen, um Ihre Lieblingsspiele zu spielen. Die Wahl der besten Hauptplatine für Ihr System bestimmt unter anderem die Größe des Gehäuses, das Sie verwenden werden, die Speicheroptionen und die Optionen für CPU-Upgrades im weiteren Verlauf. Auch wenn es heutzutage keine großen Unterschiede mehr zwischen Motherboards gibt, die auf demselben Chipsatz basieren, ist es dennoch wichtig, das Motherboard zu wählen, das für Sie und Ihre Anforderungen geeignet ist. Heutzutage ist es mehr eine Frage der Funktionen als der Leistung. Grundsätzlich hängt die Wahl des Motherboards von der Unterstützung des CPU-Sockels, den Anschlüssen, der Größe und der allgemeinen…

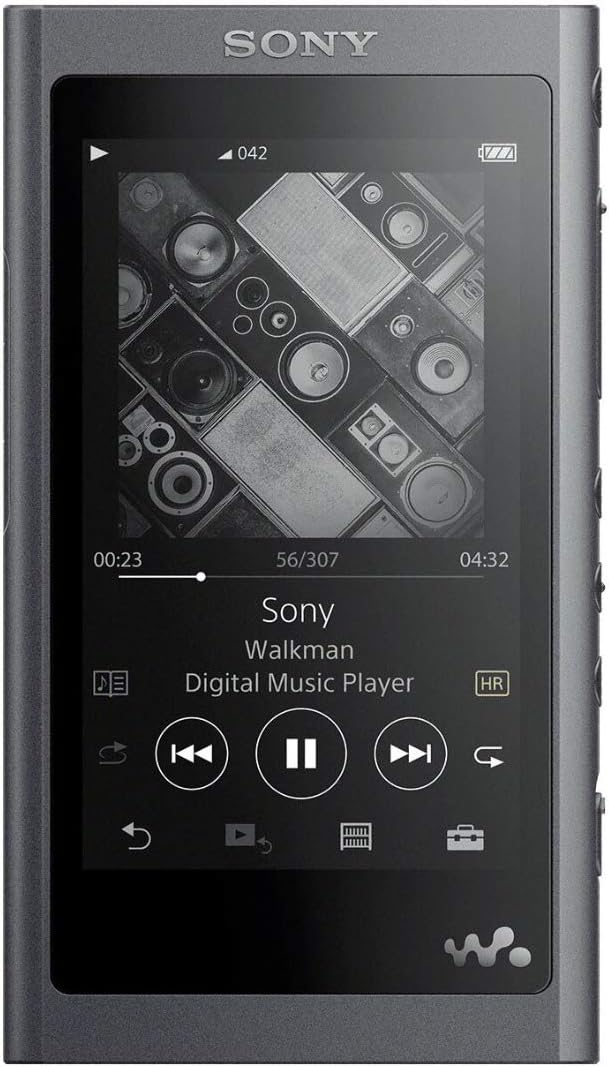

Enthüllung des Sony NW-A55: Ein Walkman-Test

In einer Ära, in der Streaming die Musiklandschaft dominiert, ruft uns ein nostalgisches Flüstern aus der Vergangenheit zurück zum greifbaren Charme physischer Medien. Hier kommt der Sony NW-A55 ins Spiel, eine moderne Reinkarnation des kultigen Walkman, die uns dazu einlädt, die Freude am persönlichen Musikgenuss neu zu entdecken. Dieser Testbericht befasst sich mit Sonys neuestem Angebot und enthüllt, wie dieses schlanke Gerät Vintage-Appeal mit modernster Technologie verbindet. Seien Sie dabei, wenn wir herausfinden, ob der Sony NW-A55 unsere musikalischen Reisen im heutigen digitalen Zeitalter neu definieren kann. Erforschung der Klangqualität Wenn man sich mit der Klangqualität des Sony NW-A55 beschäftigt, ist man sofort von der Klarheit und Fülle beeindruckt, die dieser moderne Walkman bietet. Das Gerät verfügt über eine hochauflösende Audiowiedergabe mit Unterstützung für Formate wie FLAC, WAV und MP3, so dass der Hörer jede Nuance seiner Musiksammlung genießen kann. Ob tiefe Bässe oder knackige Höhen – Sony hat diesen…

Bluetooth und LDAC: Die Geheimwaffe des Sony Walkman

Im Bereich der tragbaren Audiogeräte sticht der Walkman von Sony hervor, der Bluetooth und LDAC-Technologie als Geheimwaffe nutzt. Diese leistungsstarke Kombination sorgt dafür, dass Musikliebhaber auch unterwegs eine hochauflösende Klangqualität genießen können, die jedes Hörerlebnis in eine Klangreise verwandelt.

Die besten Sony Walkman-Modelle für Audiophile

In der sich ständig weiterentwickelnden Welt des persönlichen Audios genießen nur wenige Geräte so viel Anerkennung wie der Sony Walkman. Dieser legendäre tragbare Musikplayer, der Anfang der 1980er-Jahre auf den Markt kam, revolutionierte unser Klangerlebnis unterwegs und verwandelte unsere täglichen Fahrten zur Arbeit und gemütliche Spaziergänge in persönliche Konzerte. Auch heute noch begeistert der Walkman Audiophile und verbindet die vielfältigen Facetten der Musik mit fortschrittlicher Technologie und überragender Klangqualität. In diesem Artikel stellen wir die besten Sony Walkman-Modelle für anspruchsvolle Hörer vor und präsentieren Optionen, die nicht nur dem geschichtsträchtigen Erbe der Marke Tribut zollen, sondern auch die Grenzen der Klangtreue erweitern. Ob begeisterter Sammler oder Einsteiger auf der Suche nach exzellentem Klang – entdecken Sie mit uns eine Auswahl an Walkmans, die Innovation und Leidenschaft für Musik perfekt verbinden. Die klangliche Exzellenz des Sony Walkman für AudiophileDas Erbe des Sony Walkman lebt in den Herzen von Audiophilen weiter und…